### SANDIA REPORT

SAND2016-9613 Unlimited Release Printed September, 2016

# Hierarchical Task-Data Parallelism using Kokkos and Qthreads

H. Carter Edwards, Stephen L. Olivier, Greg E. Mackey, Kyungjoo Kim, Michael Wolf, George W. Stelle, Jonathan W. Berry, Sivasankaran Rajamanickam

Level.

Prepared by Sandia National Laboratories Albuquerque, New Mexico 87185 and Livermore, California 94550

Sandia National Laboratories is a multi-mission laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000.

Approved for public release; further dissemination unlimited.

Issued by Sandia National Laboratories, operated for the United States Department of Energy by Sandia Corporation.

**NOTICE:** This report was prepared as an account of work sponsored by an agency of the United States Government. Neither the United States Government, nor any agency thereof, nor any of their employees, nor any of their contractors, subcontractors, or their employees, make any warranty, express or implied, or assume any legal liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represent that its use would not infringe privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise, does not necessarily constitute or imply its endorsement, recommendation, or favoring by the United States Government, any agency thereof, or any of their contractors. The views and opinions expressed herein do not necessarily state or reflect those of the United States Government, any agency thereof, or any of their contractors.

Printed in the United States of America. This report has been reproduced directly from the best available copy.

Available to DOE and DOE contractors from U.S. Department of Energy Office of Scientific and Technical Information P.O. Box 62 Oak Ridge, TN 37831

| Telephone:       | (865) 576-8401             |

|------------------|----------------------------|

| Facsimile:       | (865) 576-5728             |

| E-Mail:          | reports@adonis.osti.gov    |

| Online ordering: | http://www.osti.gov/bridge |

Available to the public from U.S. Department of Commerce National Technical Information Service 5285 Port Royal Rd Springfield, VA 22161

Telephone:(800) 553-6847Facsimile:(703) 605-6900E-Mail:orders@ntis.fedworld.govOnline ordering:http://www.ntis.gov/help/ordermethods.asp?loc=7-4-0#online

SAND2016-9613 Unlimited Release Printed September, 2016

## Hierarchical Task-Data Parallelism using Kokkos and Qthreads

H. Carter Edwards, Scalable Algorithms

Stephen L. Olivier, Scalable System Software

Greg E. Mackey, Cyber Initiatives

Kyungjoo Kim, Computational Mathematics

Michael Wolf, Scalable Algorithms

George W. Stelle, Scalable System Software

Jonathan W. Berry, Discrete Math & Optimization

Sivasankaran Rajamanickam, Scalable Algorithms

Sandia National Laboratories

P.O. Box 5800 / MS 1318

Albuquerque, NM 87185

#### Abstract

This report describes a new capability for hierarchical task-data parallelism using Sandia's Kokkos and Qthreads, and evaluation of this capability with sparse matrix Cholesky factorization and social network triangle enumeration mini-applications. Hierarchical task-data parallelism consists of a collection of tasks with executes-after dependences where each task contains data parallel operations performed on a team of hardware threads. The collection of tasks and dependences form a directed acyclic graph of tasks – a *task DAG*. Major challenges of this research and development effort include: portability and performance across multicore CPU; manycore Intel Xeon Phi, and NVIDIA GPU architectures; scalability with respect to hardware concurrency and size of the task DAG; and usability of the application programmer interface (API).

### Acknowledgment

This work was funded by the Sandia National Laboratories' Laboratory Directed Research and Development (LDRD) program in the Computer and Information Science investment area.

We appreciate NVIDIA providing pre-release access to their nvcc v8.0 compiler and linker, which was critical for porting to NVIDIA's GPU architecture.

# Contents

| 1        | Intr | oducti  | on                                                       | 13 |

|----------|------|---------|----------------------------------------------------------|----|

|          | 1.1  | Conce   | pts and Terminology                                      | 14 |

|          | 1.2  | Kokko   | s / Qthreads Integration                                 | 16 |

|          | 1.3  | Mini-A  | Applications                                             | 16 |

| <b>2</b> | Dyr  | namic ' | Task DAG Abstractions, Requirements, and Lessons Learned | 17 |

|          | 2.1  | Life-cy | vcle of a Task in a Dynamic Task DAG                     | 17 |

|          |      | 2.1.1   | An Abstract Perspective                                  | 17 |

|          |      | 2.1.2   | An Illustrative Code Perspective                         | 19 |

|          | 2.2  | Lessor  | as Learned and Evolving Abstractions                     | 21 |

|          |      | 2.2.1   | Spawning and Dependences                                 | 21 |

|          |      | 2.2.2   | Compatibility of Serial and Thread Team Tasks            | 22 |

|          |      | 2.2.3   | Memory Management – Thread Scalability                   | 22 |

|          |      | 2.2.4   | Memory Management – Task Scalability                     | 22 |

|          |      | 2.2.5   | Memory Management – Task Lifetime                        | 23 |

|          |      | 2.2.6   | Critical Paths and Short Paths                           | 24 |

|          |      | 2.2.7   | CUDA Porting                                             | 24 |

|          |      | 2.2.8   | GPU Thread Team                                          | 24 |

|          | 2.3  | Final 1 | Peer Review – Nomenclature Revisions                     | 25 |

| 3        | Tas  | k Sche  | dulers and Runtime Systems                               | 27 |

|          | 3.1  | Qthrea  | ads Back-end                                             | 27 |

|          | 3.2  | Protot  | ype Kokkos Serial, Pthreads, and CUDA implementations    | 29 |

|   | 3.3  | Final   | Kokkos Serial, OpenMP, and CUDA implementations | 29 |

|---|------|---------|-------------------------------------------------|----|

|   |      | 3.3.1   | Managing Task DAG Queues                        | 30 |

|   |      | 3.3.2   | Executing a Task DAG                            | 33 |

|   | 3.4  | Portal  | ble and Thread Scalable Memory Pool             | 38 |

|   |      | 3.4.1   | Design and Implementation                       | 39 |

|   |      | 3.4.2   | Superblock States                               | 41 |

|   |      | 3.4.3   | Allocation                                      | 44 |

|   |      | 3.4.4   | Switching Superblocks                           | 45 |

|   |      | 3.4.5   | Deallocation                                    | 46 |

|   |      | 3.4.6   | Empty                                           | 46 |

| 4 | Inte | egratio | n with the Multithreaded Graph Library (MTGL)   | 49 |

|   | 4.1  | Introd  | uction to the MTGL                              | 49 |

|   | 4.2  | Graph   | abstractions in the MTGL                        | 50 |

|   | 4.3  | The N   | ITGL API                                        | 52 |

|   |      | 4.3.1   | Sizes, descriptors, and iterators               | 52 |

|   |      | 4.3.2   | Atomics and concurrency                         | 53 |

|   |      | 4.3.3   | Generic functions                               | 53 |

|   |      | 4.3.4   | Basic functionality                             | 54 |

|   |      |         | Basic MTGL include files                        | 54 |

|   |      |         | Starting out: typedefs and graph initialization | 54 |

|   |      |         | Declaring iterators and property maps           | 55 |

|   |      |         | Initialization and use of property maps         | 56 |

|   |      |         | Device computations on property maps            | 56 |

|   | 4.4  | MTGI    | L library algorithms                            | 58 |

|   |      | 4.4.1   | Breadth-First Search                            | 59 |

|   |      | 4.4.2   | Connected Components                            | 60 |

|   | 4.5 | MTGI    | Kokkos algorithm performance                    | 61 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 4.5.1   | Basic array processing                          | 61 |

|   |     | 4.5.2   | Graph Iteration                                 | 62 |

|   |     | 4.5.3   | Graph algorithm performance                     | 62 |

|   | 4.6 | Custor  | mizing MTGL algorithms to optimize Kokkos usage | 64 |

|   | 4.7 | Proces  | sing graphs that don't fit on device            | 65 |

| 5 | Tac | ho: Sp  | arse Incomplete Cholesky Factorization          | 67 |

|   | 5.1 | Introd  | uction                                          | 67 |

|   | 5.2 | Tacho   | Task Parallel Sparse Factorization              | 68 |

|   |     | 5.2.1   | 2D Sparse Block Matrix                          | 69 |

|   |     | 5.2.2   | Cholesky-by-blocks                              | 71 |

|   |     | 5.2.3   | Implementation Details using Kokkos Task API    | 75 |

|   | 5.3 | Perfor  | mance Evaluation                                | 77 |

|   |     | 5.3.1   | Task Parallel Cholesky-by-blocks Factorization  | 77 |

|   | 5.4 | Summ    | ary                                             | 81 |

| 6 | min | iTri: A | A Data Analytics Mini-Application               | 83 |

|   | 6.1 | Backg   | round                                           | 83 |

|   |     | 6.1.1   | Linear Algebra Primitives for Graph Algorithms  | 83 |

|   |     | 6.1.2   | miniTri: A Data Analytics Miniapp               | 84 |

|   | 6.2 | Task-I  | Parallel miniTri Overview                       | 85 |

|   |     | 6.2.1   | Challenges with Linear Algebra Based miniTri    | 85 |

|   |     | 6.2.2   | Task-Parallel Linear Algebra Based miniTri      | 86 |

|   | 6.3 | Task-I  | Parallel Kokkos/Qthreads miniTri Implementation | 87 |

|   |     | 6.3.1   | General Implementation Details                  | 87 |

|   |     | 6.3.2   | Kokkos Task-Parallel Functionality              | 88 |

|              |     | 6.3.3 Dynamic Task Dependencies of miniTri | 88 |

|--------------|-----|--------------------------------------------|----|

|              | 6.4 | Results                                    | 89 |

|              | 6.5 | Conclusions/Lessons Learned                | 91 |

| 7 Conclusion |     | clusion                                    | 95 |

|              | 7.1 | Goals and Key Results                      | 95 |

|              | 7.2 | Continued R&D                              | 96 |

# List of Figures

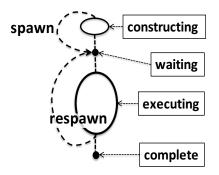

| 2.1  | Task state transitions for spawn and respawn operations       | 18 |

|------|---------------------------------------------------------------|----|

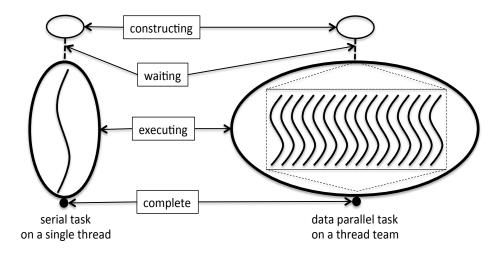

| 2.2  | Tasks execute serial or data parallel                         | 19 |

| 2.3  | Obligatory example of pure-task based Fibonacci function      | 20 |

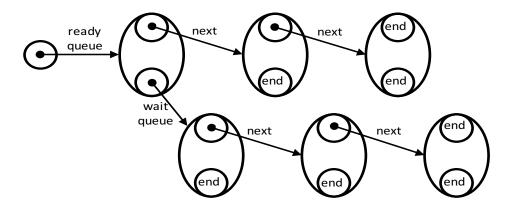

| 3.1  | Task queue linked lists                                       | 30 |

| 3.2  | Summary atomic linked list push                               | 31 |

| 3.3  | Summary of almost-atomic linked list pop                      | 31 |

| 3.4  | Scheduling a task entity                                      | 32 |

| 3.5  | Scheduling a when-all entity                                  | 32 |

| 3.6  | Completing a task or when-all entity                          | 33 |

| 3.7  | CPU hardware thread team synchronization                      | 35 |

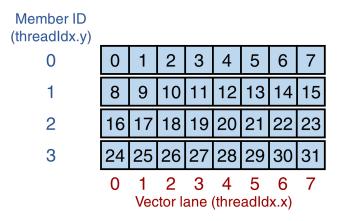

| 3.8  | GPU warp is divided into thread team members and vector lanes | 37 |

| 3.9  | Team and vector levels of parallel operations                 | 37 |

| 3.10 | Memory Pool Allocator API                                     | 38 |

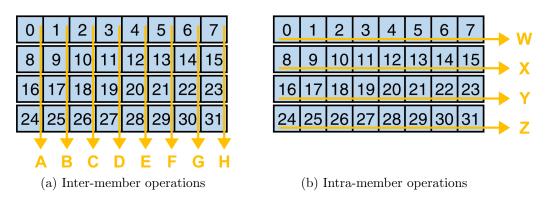

| 3.11 | Superblock State                                              | 42 |

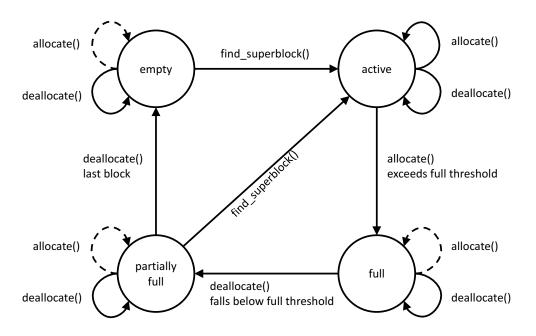

| 4.1  | The compressed sparse row graph data structure                | 50 |

| 4.2  | A typical MTGL algorithm signature                            | 51 |

| 4.3  | Calling an MTGL algorithm                                     | 51 |

| 4.4  | basic MTGL includes and namespace                             | 54 |

| 4.5  | a typical MTGL test program: header information               | 55 |

| 4.6  | declaring MTGL graph iterators and property maps              | 55 |

| 4.7  | MTGL property map access via generic function                 | 56 |

| 4.8  | MTGL property map access with Kokkos parallel primitives      | 56 |

| 4.9                                                                                       | applying a functor to an MTGL property map                                                                                                                                                                  | 57                                                                                             |

|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| 4.10                                                                                      | linear_recurrence functions                                                                                                                                                                                 | 57                                                                                             |

| 4.11                                                                                      | vertex and edge reductions with temporary functions                                                                                                                                                         | 58                                                                                             |

| 4.12                                                                                      | vertex and edge reductions with functors                                                                                                                                                                    | 58                                                                                             |

| 4.13                                                                                      | calling the MTGL breadth_first_search                                                                                                                                                                       | 60                                                                                             |

| 4.14                                                                                      | defining the visitor for MTGL breadth_first_search                                                                                                                                                          | 60                                                                                             |

| 4.15                                                                                      | finding connected components with the MTGL "shiloach_vishkin" algorithm .                                                                                                                                   | 61                                                                                             |

| 4.16                                                                                      | Team-level MTGL library coding                                                                                                                                                                              | 65                                                                                             |

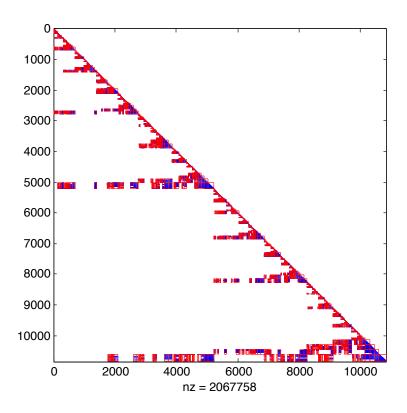

| 5.1                                                                                       | 2D Sparse block layout on a matrix (msc10848) selected from the UF collection.                                                                                                                              | 69                                                                                             |

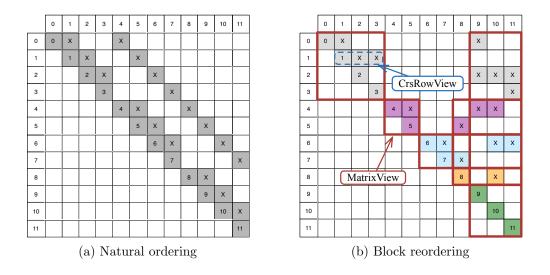

| 5.2                                                                                       | A simplified example of symmetric block nested dissection ordering permuted<br>by Scotch. Left: a given sparse matrix with its natural ordering. Right: a 2D<br>sparse block layout on the reordered matrix | 70                                                                                             |

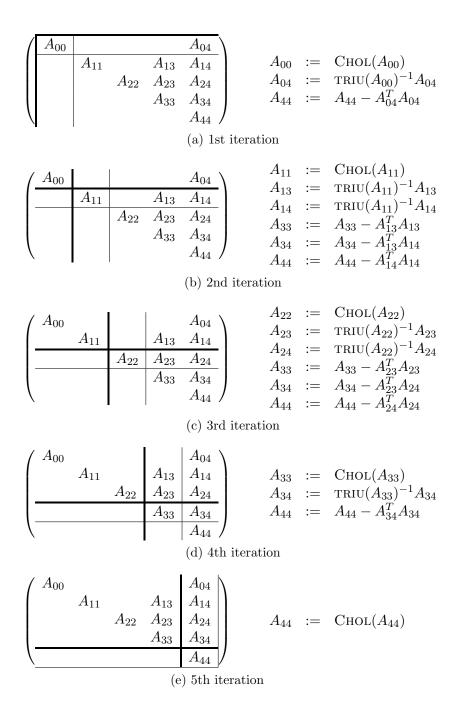

| 5.3                                                                                       | Cholesky algorithm. The blocks in the $2 \times 2$ and $3 \times 3$ block matrices that correspond to each other are of the same color. CHOL and TRIU represent                                             |                                                                                                |

|                                                                                           | Cholesky factorization and the upper triangular part of an input matrix re-<br>spectively                                                                                                                   | 71                                                                                             |

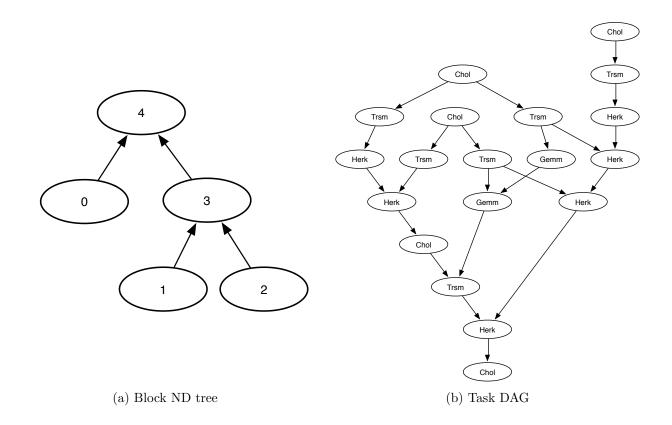

| 5.4                                                                                       | · - · · -                                                                                                                                                                                                   | 71<br>72                                                                                       |

| $5.4 \\ 5.5$                                                                              | spectively.                                                                                                                                                                                                 |                                                                                                |

|                                                                                           | spectively                                                                                                                                                                                                  | 72                                                                                             |

| 5.5                                                                                       | spectively                                                                                                                                                                                                  | 72<br>74                                                                                       |

| 5.5<br>5.6                                                                                | spectively                                                                                                                                                                                                  | 72<br>74<br>75                                                                                 |

| 5.5<br>5.6<br>5.7                                                                         | spectively                                                                                                                                                                                                  | 72<br>74<br>75<br>75                                                                           |

| <ol> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol>               | spectively                                                                                                                                                                                                  | 72<br>74<br>75<br>75<br>76                                                                     |

| <ol> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> </ol>               | spectively                                                                                                                                                                                                  | <ul> <li>72</li> <li>74</li> <li>75</li> <li>75</li> <li>76</li> <li>79</li> </ul>             |

| <ol> <li>5.5</li> <li>5.6</li> <li>5.7</li> <li>5.8</li> <li>5.9</li> <li>5.10</li> </ol> | spectively                                                                                                                                                                                                  | <ul> <li>72</li> <li>74</li> <li>75</li> <li>75</li> <li>76</li> <li>79</li> <li>80</li> </ul> |

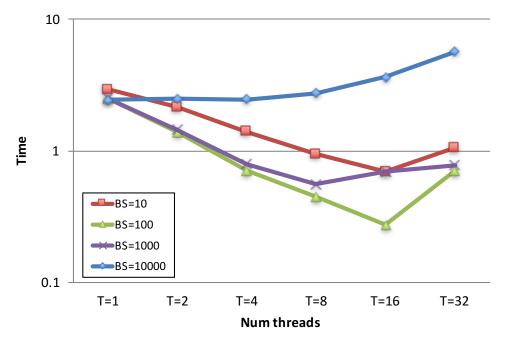

| 6.4 | Run times (in s) miniTri run times (in s) for Oregon-1 graph for Kokkos/Qthreads implementation for different block size.                                   |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

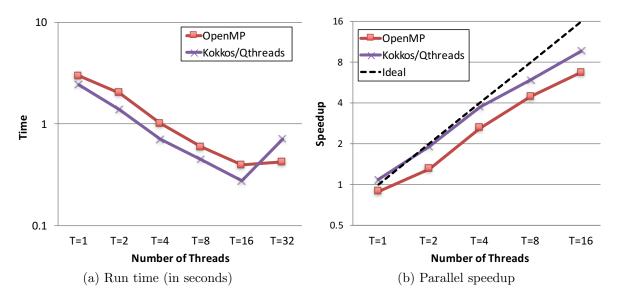

| 6.5 | Comparison of OpenMP and Kokkos/Qthreads miniTri implementations for<br>Oregon-1 graph (best block size for both methods shown)                             | 91 |

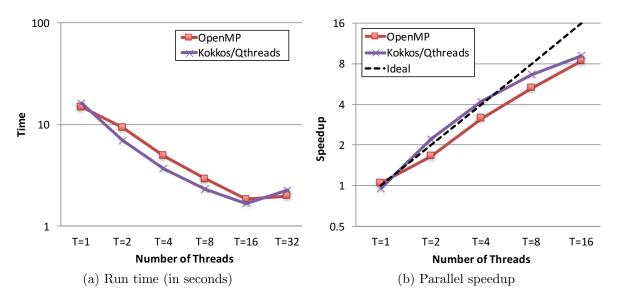

| 6.6 | Comparison of OpenMP and Kokkos/Qthreads miniTri implementations for<br>email-Enron graph (best block size for both methods shown)                          | 92 |

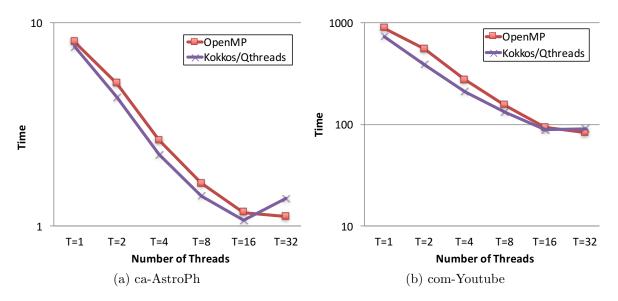

| 6.7 | Comparison of miniTri run times (in seconds) for ca-AstroPh and com-Youtube graphs: OpenMP versus Kokkos/Qthreads (best block size for both methods shown). | 93 |

# List of Tables

| 4.1 | MTGL Types, Descriptors, Iterators, and Categories                                                                                                                                                | 52 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | MTGL Breadth-first search visitor API                                                                                                                                                             | 59 |

| 4.3 | Basic Kokkos data parallelism through the MTGL interface                                                                                                                                          | 61 |

| 4.4 | Data parallelism and graph iteration                                                                                                                                                              | 62 |

| 4.5 | Datasets for MTGL library algorithm experiments                                                                                                                                                   | 63 |

| 4.6 | MTGL breadth-first search performance                                                                                                                                                             | 63 |

| 4.7 | MTGL PageRank performance                                                                                                                                                                         | 63 |

| 4.8 | MTGL connected components performance                                                                                                                                                             | 64 |

| 5.1 | Test problems selected from the UF sparse matrix collection                                                                                                                                       | 77 |

| 5.2 | Number of nonzero Cholesky factors resulting from level(k) symbolic factoriza-<br>tion; for comparison, the last column shows the number of fill from complete<br>factorization with AMD ordering | 78 |

| 6.1 | Datasets                                                                                                                                                                                          | 90 |

# Chapter 1

# Introduction

To sustain scalability on emerging manycore computing architectures (Terascale workstations, Petascale clusters, and Exascale supercomputers) our analysis codes must exploit all opportunities for manycore parallelism. Migrating applications to manycore architectures currently requires scientists and engineers to (1) have detailed knowledge of vendor-specific performance characteristics and constraints, (2) obfuscate essential mathematics in their codes with parallel processing directives, and (3) generate and maintain multiple versions of codes to meet vendor-specific performance requirements. Even vendor-neutral programming models (OpenMP, OpenACC, OpenCL) require architecture-specific knowledge to achieve acceptable performance and pollute mathematical code with parallel processing directives.

Two key R&D projects at Sandia address independent facets of manycore parallelism. Qthreads [1] addresses task parallelism with highly efficient task scheduling algorithms. Kokkos [2] addresses data and vector parallelism through a performance portable interface that minimizes users exposure to architecture-specific details. In this project we integrate these R&D efforts to create a hierarchical task-data parallel capability that is performance portable across manycore architectures. The application programmer interface (API) for this capability is an enhancement of the Kokkos library and the implementation of this capability utilizes an enhancement of the Qthreads library and its task scheduling algorithms.

Our productivity goal is to enable scientists and engineers to program emerging manycore architectures with neither extensive architecture-specific knowledge nor ubiquitous parallel processing directives. This capability should be general and applicable to diverse application domains. We evaluate this *generality* goal by exercising the integrated Kokkos / Qthreads libraries across high performance computing (HPC) domains of consequence to Sandia. For the simulation domain we develop a hierarchical task-data sparse matrix factorization computational kernel used in the solution of sparse linear systems. For the analytics domain we develop a new port of Sandia's Multithreaded Graph Library (MTGL) using the enhanced Kokkos interface.

### 1.1 Concepts and Terminology

The goal of our R&D is to create new capability for a shared memory directed acyclic graph (DAG) of tasks with internal data parallelism that is easily accessible to application developers (our users). This goal-statement is densely packed with concepts and terminology elaborated as follows.

**Task:** A *task* is an application's computation that is given to a runtime system for subsequent execution. A task is implemented as a function and parameters with which the function operates. A runtime system can execute independent tasks in parallel on hardware threads of a multicore CPU or manycore GPU.

**Dependences and Task DAG:** A task may have an "executes after" dependence on one or more other tasks. For example, when task **B** inputs data that is output by task **A** then task **B** must execute after task **A** completes. The collection of tasks and dependences defines a graph where tasks are graph-vertices and dependences are directed graph-edges. This graph cannot contain cycles of dependences, otherwise tasks within the cycle could never be executed. We refer to the parallel execution of a collection of tasks where the inter-task executes-after dependences are enforced as the *task DAG* parallel pattern. In a traditional task DAG parallel pattern each task executes on a single hardware thread and is thus internally serial.

**Data Parallel Task on a Thread Team:** New manycore architectures have an increasing number of hardware threads where groups of hardware threads share critical hardware resources such as registers and L1 cache. For example, the four hyperthreads of the Intel Xeon Phi architecture and the "warp lanes" of an NVIDIA GPU architecture define a tightly bound group of hardware threads. When these tightly bound hardware threads execute different tasks computing on different data they will compete for shared resources, which typically results in degraded performance compared to one of the hardware threads executing the same tasks sequentially. To effectively use the parallelism offered by tightly bound hardware threads a task should execute on that entire group and utilize the group as a well-coordinated *thread team*. Thread-team coordination is most easily managed and expressed through data parallel operations such as parallel\_for, parallel\_reduce, or parallel\_scan. Thus a task DAG will be most performant on new manycore architectures when tasks run on thread teams with internal data parallelism. The first innovation of our R&D is to support tasks with internal data parallel operations running on thread teams.

**Execution Space and Task Policy:** A heterogeneous compute node has multiple resources for executing computations; for example, the NUMA regions of multicore CPUs and attached GPUs. Kokkos refers to a resource *where* parallel computations may execute as an *execution space* and the rules or algorithms for *how* to schedule those computations as an

*execution policy.* Thus, in Kokkos' nomenclature we name a runtime system which manages, schedules, and executes a task DAG as a *task execution policy*, or more succinctly as a *task policy*, on an execution space.

**Spawning and Future:** Spawning is the process of creating a task and inserting it into a task policy for future execution. When a task is spawned a task policy returns a handle for that task, referred to as a *future*. Futures are used to express task dependences and obtain simple return values from completed tasks. For example, an application spawns task  $\mathbf{A}$  and then spawns task  $\mathbf{B}$  with an executes-after dependence on task  $\mathbf{A}$ . When task  $\mathbf{B}$  is created, it may be given a future referencing task  $\mathbf{A}$  so that when task  $\mathbf{B}$  executes it can query the return value from task  $\mathbf{A}$ .

**Dynamic Task DAG:** A task DAG implementation may require that the complete task DAG be constructed before any task within the task DAG can execute – we refer to this as a *static* task DAG. We require a *dynamic* task DAG where an executing task may spawn new tasks with new dependences. This dynamic task DAG requirement posed significant design and implementation challenges for the GPU execution space, scalability with respect to the number of hardware threads, and scalability with respect to the size of the task DAG. The second innovation of our R&D is to support the dynamic task DAG parallel pattern on a GPU execution space.

Respawn and Non-blocking (non-waiting) Tasks: In a traditional task DAG parallel pattern when a task spawns another task it may wait for that spawned task to complete. Such a wait operation defines an implicit dependence – the waiting task blocks and can only resume executing after the spawned task completes. In order to guarantee that execution of the overall task DAG will make progress a blocked task must relinquish its execution resource so that other tasks can execute on that resource. Considerable runtime mechanisms are required to support blocking and relinquishing execution resources. Supporting blocking and relinquishing resources adds complexity, memory overhead, and runtime overhead to task scheduling and execution. We deemed that this complexity and overhead is unacceptable for the intended HPC algorithms and may not even be feasible to implement for lightweight GPU cores. Instead of a wait operation we provide the *respawn* operation by which an executing task can re-insert itself into the task DAG with new dependences. The respawn operation causes an executing task, upon returning from its function, to be rescheduled for subsequent execution when its new dependences have completed. Thus a traditional operation of task **B** waiting on task **A** can be replaced by task **B** respawning itself with a new dependence on task A and then returning. The third innovation of our R&D is the respawn replacement for the traditional wait operations in a dynamic task DAG.

**Task Priority:** An application's task DAG algorithm may have knowledge of task DAG branches that are in the critical path for completion of the algorithm. An algorithm may

direct the task policy to prioritize execution of tasks in the critical path to more quickly complete the whole algorithm. An algorithm may also prioritize tasks to manage peak memory consumption during task DAG execution.

**Memory Pool Allocator:** A dynamic task DAG allocates and deallocates memory for tasks and dependences while tasks are executing in parallel. Significant challenges for dynamic memory management are portability to the GPU execution space and scalability with respect to the number of threads concurrently allocating and deallocating memory. Memory allocation and deallocation by the GPU runtime from within a GPU function uses a fixed pool of memory that is allocated on the host before the GPU function can be launched. The fourth innovation of our R&D is a portable and thread scalable memory pool allocator used by the dynamic task DAG runtime on GPUs and other execution spaces.

### 1.2 Kokkos / Qthreads Integration

Execution policies, thread teams, and data parallelism are existing Kokkos capabilities. Our R&D extends these capabilities for the dynamic task DAG parallel pattern. Scheduling tasks with dependences and executing tasks on a single hardware thread are existing Qthreads capabilities. Our R&D extends these capabilities to support executing a given task on a team of hardware threads. We integrate Qthreads as an additional *back-end* to Kokkos (alongside Kokkos' existing back-ends OpenMP, pthreads, and CUDA back-ends) to enable a Kokkos-based interface for tasks. We also apply Qthreads' task management and scheduling strategies to implement in other Kokkos back-ends the "dynamic task DAG with internally data parallel tasks" pattern.

### **1.3** Mini-Applications

The developed task DAG capability is evaluated with two mini-applications. The sparse matrix Cholesky factorization mini-application uses a blocked algorithm to define a task DAG of submatrix computations. The triangle enumeration mini-applications defines a task DAG to concurrently find and analyze triangle-cycles within a social network graph.

# Chapter 2

# Dynamic Task DAG Abstractions, Requirements, and Lessons Learned

A program begins in a single host process thread which typically invokes the program's main function. In an HPC application this host process thread typically calls a message passing interface (MPI) library's initialize function and obtains an MPI communicator for subsequent distributed memory parallel operations. The Kokkos and Qthreads libraries are solely concerned with shared memory parallel operations, and as such are decoupled from distributed memory parallel operations.

A host thread process initializes Kokkos, which in turn initializes one or more backends that execute parallel computations within execution spaces. One of these back-ends uses Qthreads to execute parallel computations on CPU and Intel Xeon Phi architectures. Initialization acquires execution resources (*e.g.*, hyperthreads, attached GPU) on which subsequent intra-node parallel operations execute. These include simple data parallel operations (*e.g.*, parallel\_for over a range [i, j)), hierarchical data parallel operations using thread teams, and hierarchical task-data parallel operations.

### 2.1 Life-cycle of a Task in a Dynamic Task DAG

The life-cycle of a task in a dynamic task DAG is presented from an abstract perspective with diagrams and specifications, and then again from an illustrative code perspective.

#### 2.1.1 An Abstract Perspective

A user's task is implemented by a *closure* with the states and life cycle illustrated in Figures 2.1 and 2.2. A closure is either a C++ functor which is a C++ class that has a member function with specified calling arguments, or C++11 lambda expression which is an anonymous functor that is automatically generated by the C++ compiler. The observable states of a task are constructing, waiting, executing, and complete.

A spawn operation allocates memory, constructs, and inserts a task into a task policy's

Figure 2.1: Task state transitions for spawn and respawn operations. When a user spawns a task it is allocated, constructed, and insert into a task policy's collection of waiting tasks. When a user respawns an existing task it is re-inserted into a task policy's collection of waiting tasks.

collection of waiting tasks. The spawn operation calls a functor's class constructor or invokes the lambda's capture mechanism within the thread that performs the spawn operation. While the class constructor or lambda capture is executing the task is in the constructing state After the construction finishes a spawn operation inserts the task into the task policy's collection of waiting tasks, and the task is in the waiting state. A task may be spawned with one or more execute-after dependences. A task is in the waiting state is either waiting on its dependences to complete or is ready to execute and waiting for the task policy to select the task for execution.

A task policy selects a task A that is waiting and ready to execute. The task's execution function, the C++ operator() member function with the required calling arguments, is called in the designated execution space. While this function is executing the task is in the executing state. If this function returns without having requested to be respawned the task policy completes task A by (1) updating any tasks waiting on task A and (2) destroying and deallocating task A if no futures or dependences exist that reference task A. A task that is not deallocated but has completed execution is in the complete state.

During its execution task A may request to be respawned with or without new dependences. In this case, when task A's execution function returns the task policy will re-insert task A into the collection of waiting tasks.

A task policy executes a serial task on a single thread and executes a data parallel task on a thread team (Figure 2.2). When a data parallel task executes its execution function is called by each member of the thread team and the task's C++ class instance or lambdacapture is shared by all threads of the thread team. These threads are guaranteed to execute concurrently. Thus a data parallel task's execution function must be carefully implemented to avoid concurrent access race conditions on the shared task data. For example, only one member of the task's thread team should request a respawn for the task.

Figure 2.2: Tasks execute serial or data parallel. A task policy selects a task that is ready to execute from the waiting collection and executes the task on a single thread or thread team. If the task does not respawn when the task finishes executing it is complete.

#### 2.1.2 An Illustrative Code Perspective

We repeat the overview of a task states and lifecycle, this time elaborating from an illustrative code perspective. For this illustration we use the obligatory Fibonacci function with the naive, purely task based implementation presented in Figure 2.3. While this example is an extremely inefficient implementation of the Fibonacci function, it provides an appropriately simple code-based illustration of our task DAG abstractions and mechanisms.

The fibonacci function first constructs a TaskPolicy object (Fig. 2.3 line #6). A task policy executes tasks in an execution space that is specified by the task policy's ExecSpace template argument. A task policy supports dynamic memory allocation and deallocation for task memory through a thread scalable memory pool within a memory space. The memory space and size of this memory pool are arguments to the task policy constructor.

The host process calls the host\_spawn function to spawn the initial f(N) task and obtain a Future which references the spawned task (Fig. 2.3 line #7). The spawn function is given a FibonacciTask functor and the TaskSingle parameter indicating a single thread task. Spawning a task from the host process has different implementation considerations than spawning a task from within an executing task. For example, the mechanism for capturing the task's execution function is different when spawning from the host process or within a GPU task. The host process then waits for *all* ready tasks contained within in the task policy to complete (Figure 2.3 line #8). The task policy may not execute any tasks until the host process calls the wait function (Fig. 2.3 line #8). For example, when using a GPU execution space the wait function launches a GPU kernel to execute the task DAG. Once the all ready tasks in the task policy have completed the wait function returns and the f(N) task's future is queried for the resulting value (Fig. 2.3 line #9).

```

1

template< typename ExecSpace >

2

long fibonacci( long n )

3

{

4

using memory_space = typename ExecSpace::memory_space ;

const size_t memory_pool_size = /* ... */ ;

5

6

TaskPolicy< ExecSpace > P( memory_space() , memory_pool_size );

Future< ExecSpace , long > F = P.host_spawn( FibonacciTask(P,n), TaskSingle );

7

8

wait( P );

9

return F.get();

10

11

12

template< typename ExecSpace >

13

struct FibonacciTask {

14

using value_type = long ;

15

16

using policy_type = TaskPolicy<ExecSpace> ;

using future_type = Future<ExecSpace,value_type> ;

17

18

using member_type = typename policy_type::member_type ;

19

20

policy_type P ;

21

future_type child[2] ;

22

value_type N ;

23

24

void operator()( const member_type & , value_type & result )

25

26

if (N < 2) \{ result = N; \}

27

else if ( child[0].is_null() ) {

28

child[0] = P.task_spawn( FibonacciTask(P,N-1), TaskSingle );

child[1] = P.task_spawn( FibonacciTask(P,N-2), TaskSingle , TaskHighPriority );

29

30

P.respawn( this , P.when_all(2, child), TaskLowPriority );

31

}

32

else {

33

result = child[0].get() + child[1].get();

34

}

35

}

36

37

FibonacciTask( const policy_type & argP , long argN )

38

: P(argP), child{}, N(argN) {}

39

};

```

Figure 2.3: Obligatory example of a simplistic, pure-task based Fibonacci function, f(N) = f(N-1) + f(N-2), implemented with Kokkos' dynamic task DAG functionality.

A task's resulting value is declared by the functor's value\_type (Fig. 2.3 line #15). The functor's operator() implements the task's execution function. This function is called with a task policy member and a value object in which the function outputs its result. The task policy member argument defines the context in which the task executes; for example, which member of a thread team. In the Fibonnacci illustration all tasks are single thread so the task policy member argument can be ignored.

In the Fibonacci illustration a functor's child futures are initially null – they do not reference a task. The first time a Fibonacci task is called with 2 < N wo child Fibonacci tasks (f(N-1) and f(N-2)) are spawned and their futures are saved in the child variable (Fig. 2.3 lines #28-29). Since these spawn operations occur within a running task the task\_spawn function is used instead of host\_spawn. The f(N) task cannot explicitly wait on the two spawned tasks so the f(N) task implicitly waits by requesting respawning with dependences on the child tasks (Fig. 2.3 line #30). A respawn operation declares new dependences, may declare a different priority, but cannot change the task' original single thread / thread team designation. Upon returning from its execute function the f(N) task is re-inserted into the task policy's collecton of waiting tasks.

A task may be initially spawned with  $D_0$  dependences and subsequently respawn itself K times, each time with  $D_k$  dependences. Supporting a dynamic number of dependences adds complexity and potentially degrades performance in a task DAG implementation. To maintain a simple and performant implementation a task is spawned or respawned with at most one Future. Multiple execute-after dependences are supported by creating a when\_all aggregate future (Fig. 2.3 line #30). The when\_all function returns an future that references an aggregate collection of tasks as opposed to a single task. This future is complete when all tasks in the aggregate collection are complete.

In the Fibonacci illustration a f(N) task request respanning with new dependences on f(N-1) and f(N-2) child tasks. The f(N) task is called again after the child tasks complete and their results can be queried. The second call to a f(N) task can query f(N-1) and f(N-2) result to compute its own result (Fig. 2.3 line #33). This time the task does not respawn will be complete when the execution function returns.

Selecting ready tasks for execution: Spawning or respawning a task optionally declares the task to have high, regular, or low priority; where regular priority is the default. Most of Kokkos' back-end task policies choose tasks from those that are ready to run as follows. First, when multiple tasks are ready-to-run tasks with higher priority are chosen over lower priority. Second, when priorities are equal then a last-ready-first-run strategy is used; a.k.a., a last-in-first-out (LIFO) strategy.

### 2.2 Lessons Learned and Evolving Abstractions

Research and development of the dynamic task DAG capability transpired through several prototyping iterations. Each prototype was unit tested and evaluated by using the prototype mini-applications. Evaluation was initially performed on CPU multicore architectures, then Intel Xeon Phi manycore architectures, and finally NVIDIA GPU architectures. Each iteration resulted in lessons learned regarding usability, performance, and hardware constraints; leading to design improvements and re-implementation.

#### 2.2.1 Spawning and Dependences

When spawning or respawning a task the number of dependences is not determined until at runtime. Our first prototype allocated task data when a task is spawned to accomodate a specified number of dependences. However, when initially spawned the number of dependences required for a subsequent respawn request may not be known. This became problematic because an algorithm must guess at an upper bound for respawn dependences - a usability impediment. Our lesson learned is to separate task allocation from multipledependence allocation. This is accomplished by allowing a task to have at most one direct dependence, which can be an independently allocated aggregate *when all* dependence. This allows an application to spawn and respawn tasks without concern for the number of dependences that a task may be given at some future respawn step.

#### 2.2.2 Compatibility of Serial and Thread Team Tasks

A task executing on a thread team requires a mechanism for coordinating the thread team; e.g., partitioning data parallel work among the threads of the team. In contrast, a task executing on a single thread does not have this requirement. Because of these different requirements our initial prototype design defined two different task execution function interfaces for single thread tasks and thread team tasks. This initial design was problematic for algorithms that require the flexibility to choose whether a given task was to execute on a single thread or thread team.

In our final design we define the same interface for both single thread and thread team tasks. In this interface, shown in Figure 2.3 on line #24, an execution function is always called with a thread team member\_type argument. If a task is guaranteed to be called on a single thread this argument can be ignored, as in the Fibonacci illustration. Otherwise the member\_type argument is used to coordinate thread team parallel operations.

#### 2.2.3 Memory Management – Thread Scalability

Our first prototype on a multicore CPU architecture used the runtime's standard memory allocation and deallocation functions. With the CPU's small number of hardware thread scalability was not a concern. When progressing to the Intel Xeon Phi manycore architecture these standard runtime functions became a performance problem with frequent concurrent allocation and deallocations. To call these standard allocation and deallocation functions on a GPU requires pre-allocation of a pool of memory from the host process, and this preallocation cannot be subsequently released. This is problematic because when a task DAG algorithm completes all of its allocated task memory is no longer needed but that memory cannot be released. Thus we developed a portable and thread scalable memory pool allocator through which a task DAG memory pool is allocated when the task policy is constructed and deallocated when the task policy is destructed. Details of the portable, thread scalable memory pool allocator are given in Section 3.4.

#### 2.2.4 Memory Management – Task Scalability

Integrating a memory pool into the task policy posed new challenges for our mini-applications. In the first CPU-only prototype algorithms that had access to practically unlimited memory of the large CPU node, now these algorithms had to address a fixed amount of memory for the task DAG. The first algorithmic observation is that even when the entire task DAG is huge only a small fraction of tasks are running at a given moment. An algorithm need only have enough ready tasks in the dynamic task DAG to keep all hardware threads busy executing tasks, and ensure that as executing tasks complete there are ready tasks to begin executing. Beyond this number waiting or completed tasks merely consume memory without contributing to the progress of the algorithm. Thus for scalability with respect to the end-to-end size of a task DAG an algorithm must now also consider the "high water mark" of memory allocated for tasks. This high water mark is governed by the rate at which tasks are spawned (allocated) versus the rate at which tasks are completed and then deallocated.

A task DAG algorithm can manage the rate of task spawning versus the rate of task completion by spawning a *driver* task that, when it executes, iteratively spawns the algorithm's large number of *computational* tasks. When computational tasks are spawned within an iteration the spawning rate can be "throttled" by periodically exiting the iteration, respawning the driver task at lower priority than the computational tasks, and then resuming iterative task spawning when the driver task is called again. Respawning the driver task at a lower priority guarantees that execution of the driver task will only resume when there are no higher priority computational tasks ready to execute. As long as computational tasks are deleted upon completion an algorithm can managed the task high water mark.

#### 2.2.5 Memory Management – Task Lifetime

A *static* task policy allocates all tasks and dependences before any task begins executing and does not modify or deallocate a task until all tasks have completed. In contrast a *dynamic* task policy allocates, modifies, and deallocates tasks and their dependences while other tasks are executing. In a dynamic task policy the lifetime of a task begins when a spawn operation allocates the task and ends when the task is complete and no Future exists that references that task, and the task can be deallocated. One or more futures may reference a task; therefore, these futures have shared ownership of the task along with the task policy; *i.e.*, the task's memory must be deallocated when the last TaskPolicy or Future reference is destroyed.

The closure of a task may contain futures that reference other tasks. In the Fibonacci example (Figure 2.3) the f(N) task holds futures for the f(N-1) and f(N-2) These futures, and the entire closure, are unused and unnecessary once the task completes. Furthermore, the existence of these futures prevents their associated tasks from being deallocated until the closure's C++ destructor is applied to destroy the closure. Therefore once a task is complete it associated closure is immediately destroyed even though the task's memory may not be deallocated. In the Fibonacci example this means that the C++ FibonacciTask destructors are applied to the f(N-1) and f(N-2) closures before the respawned f(N) task is executed for the second time; which allows the "child" tasks of f(N-1) and f(N-2) to be deallocated as well.

#### 2.2.6 Critical Paths and Short Paths

A task DAG algorithm may have knowledge of task DAG branches that are in a critical path for completion of the algorithm or are in a *short* path, which is likely to more quickly complete if executed. With this knowledge an algorithm can prioritize execution of tasks in the critical path to complete the algorithm more quickly, or prioritize tasks in short paths so that those tasks can be deallocated. In the Fibonacci example the f(N-2) task is spawned with higher priority than the f(N-1) task because it has a shorter path to completion and can then deallocate tasks on that branch.

#### 2.2.7 CUDA Porting

Porting to NVIDIA CUDA was the high risk "stretch goal" for our project. We anticipated the non-blocking (non-waiting) challenge and conceived the respawn strategy to portably address this constraint. We anticapated the task memory management challenge and developed the memory pool to portability address this requirement. We anticipated that separate compilation of GPU task execution functions requires the use of CUDA *relocatable device code* and managing the resulting GPU-versus-CPU function pointers. However, we did not anticipate that implementing a task policy for CUDA would push NVIDIA's nvcc compiler and linker technology to the "breaking point."

Our early simple unit tests of required CUDA features were successful using nvcc v7.5, the most recent release of nvcc. However, when the prototype task policy was ready to build the nvcc v7.5 linker was unable to link the prototype, failing with an internal error. We leveraged our collaborative relationship with NVIDIA to quickly diagnose the error – discovering that it was a known bug which would be fixed in the yet unreleased nvcc v8.0. We then heavily leveraged our long-term collabortive relationship with NVIDIA to obtain early access to a pre-release nvcc v8.0. With this version of nvcc we successfully ported to CUDA and met our high-risk "stretch goal."

We appreciate the above-and-beyond-expectations support we received from NVIDIA. Our CUDA porting stretch goal could not have been accomplished without this support.

#### 2.2.8 GPU Thread Team

Our prorotype task policy for CUDA mapped thread team tasks onto CUDA thread blocks. NVIDIA GPU hardware is designed around a performance point of thread block sizes between 128 and 512 "hardware threads," with 1 and 1024 as absolute lower and upper bounds. These hardware threads are grouped into 32-thread *warps* that effectively execute lock-step on a single instruction stream. Thus when a computation selects a block size of N the computation is assigned enough 32-thread warps to provide N threads.

We learned through our mini-applications that algorithms using hierarchical task-data parallelism with large task counts are likely to use only modest amounts of data parallelism within tasks. Thus the mapping of thread team tasks onto entire CUDA thread blocks left many GPU threads idle. As such we redesigned the CUDA task policy back-end to map thread team tasks onto warps instead of blocks.

### 2.3 Final Peer Review – Nomenclature Revisions

A final Sandia-internal peer review of the Kokkos task DAG capability and API was held on September 8, 2016. This peer review generated recommendations to revise API nomenclature and enhance functionality as follows.

In this document we refer to the component which manages the execution and lifetime of an entire task DAG as the *task policy*. The peer review recommendation is to change the name of this component to *task scheduler*, and apply the term *task policy* to how a particular task is to be executed. This nomenclature is consistent with task DAG capabilities such as in Uintah [3] and in Charm [4]. This nomenclature is also consistent with the Kokkos data parallel API where execution policies are applied when dispatching data parallel kernels.

Task thread teams are currently a fixed size that is deduced from the underlying hardware (Section 3.3.2). A requested enhancement is to allow the thread team size to be selected by the application.

# Chapter 3

# **Task Schedulers and Runtime Systems**

Task parallelism delegates responsibility for scheduling parallel computations from the application programmer to a task policy and it underlying runtime system. Design and implementation of a runtime system can have a profound effect on the efficiency and scalability of the application. An advantage of applications using Kokkos' task policies is that many different back-end implementations are available without changing the application source code. We developed several implementations described in this chapter.

### 3.1 Qthreads Back-end

The Qthreads multithreading library is a C-based API and run time system inspired by the Tera/Cray MTA/XMT architectures. Analogous to those hardware barrel-processor machines, it is designed to provide software support for many user-level tasks in flight with fast synchronization using full-empty bits (FEBs). Qthreads schedules its user-level tasks, called qthreads, onto long-lived worker pthreads that are pinned to cores in topology-aware configurations. Several different task scheduling strategies and locality-based optimizations have been developed for Qthreads, making it an attractive choice for a performant Kokkos tasking back-end.

Adapting Qthreads for use with Kokkos required the addition of some new functionality while leveraging key existing features as well. Qthreads provides performant task creation, scheduling, execution, and synchronization. Dependence resolution uses the "preconditioned task" feature, in which completions of dependences trigger the movement of tasks into ready queues in an event-driven manner. New support was needed for the "task team" concept, in which a coordinated group of tasks execute synchronously on tightly-coupled hardware resources, such as a small group of cores sharing a cache or a set of hardware threads on the same core. Qthreads scheduling had in the past been centerd on a model of singleton tasks load balanced among distributed queues by work stealing without regard for coordinating tasks (other than ensuring that dependences are fulfilled). While one solution to add the needed functionality would have been to create a new scheduler, the chosen solution was to modify the existing scheduler. Two new mechanisms were added: cloned tasks and local priority queues, described below. Note that they were incorporated into Qthreads in such a way as to be useful not only for Kokkos but also for other libraries and applications using

#### Qthreads.

**Cloned Tasks** The new task cloning facility in Qthreads allows a task to be spawned with a clone\_count parameter indicating the number of clones, i.e., identical instances, of that task to be executed. Each clone is executed independently. To implement data-parallelism in tasks, Kokkos creates a set of clones for each task corresponding to the number of threads in the team. Since the clones are executed independently, the body of each task includes synchronization among the tasks. Although cloned tasks are identical, Kokkos queries the thread identifier for the thread that is executing each task and uses that number as an index into the work (iteration space) and data (views).

Local Priority Queues The other major Qthreads capability added to support Kokkos tasking is the local priority queue. The default scheduler in Qthreads divides the available cores into locality domains, known as shepherds. Each domain has its own queue and a set of nearby threads that draw from the queue. Work stealing between the queues of the different shepherds maintains load balance even in the presence of irregular and unpredictable workloads. (Work stealing is a well-known process by which idle worker threads draw work from remote queues where more ready tasks are available.) For data-parallel Kokkos tasks, all related tasks, implemented as cloned tasks as described above, should be executed by a team of nearby threads. Thus in Qthreads such tasks should be queued and executed on the same shepherd's queue and not stolen by other shepherds' worker threads. Furthermore, each of the related (cloned) tasks should be executed simultaneously within the team of threads, each on a different worker.

In addition the default queue on each shepherd, we have added a new local priority queue. "Local" indicates that each queue is particular to a shepherd. "Priority" indicates that an idle thread within the shepherd first checks this queue for available tasks to execute before checking the shepherd's default queue. By enqueueing together the set of cloned Qthreads tasks corresponding to a data-parallel Kokkos task, the runtime ensures that all clones will remain on that shepherd and dequeued successively by each worker in the shepherd until all are executing, without dequeing any intervening unrelated tasks from the shepherd's default queue.

**Distributed Queues** One of the challenges for a task runtime is efficiently managing the increasing number of cores per NUMA domain. Having one queue in memory that all cores share creates a significant contention bottleneck. To address this issue, we've implemented a new scheduler for Qthreads that has multiple queues per NUMA domain that are shared between workers. Work is distributed across these queues uniformly, preventing a single point of contention. This approach has significant benefits for data-parallel tasks, as the sequential bottleneck of each worker dequeueing a task clone from a shared queue for a data-parallel task does not scale to large core counts. Building on the new scheduler, we've started implementing an interface for data-parallel tasks that scales better than the clone\_count

interface outlined above, to be completed with follow-on funding after the LDRD ends.

# 3.2 Prototype Kokkos Serial, Pthreads, and CUDA implementations

We developed prototypes for Kokkos' Serial (non-parallel) and Threads (using raw pthreads) to facilitate rapid evaluation of the task policy interface and design. We also developed miniapplications using these prototypes to evaluate the portability, performance, and usability of the task DAG functionality. Numerous lessons were learned and our abstractions evolved accordingly as described in Section 2.2. These lessons learned also led to significant improvements in the software design and implementation of the second generation task DAG capability developed in the final months of this LDRD.

The early Threads prototype provided an R&D framework for exploring lock free task DAG scheduling algorithms. This prototype was then ported to the Cuda back-end where race conditions were exposed, analyzed, and addressed. This initial lock free implementation enabled an in-depth analysis of the task life-cycle states, state transitions, and how to implement lock free transitions.

At the core of the prototype each task had an explicit state variable that reflected the conceptual states of a task (Figures 2.1 and 2.2). A task's state was explicitly expressed and changes to its state variable were applied atomically. We observed that the task's internal data structure had a one-for-one derived state that was also updated atomically. Thus the explicit state and the internal data structure state were redundant and maintaining both resulted in redundant atomic updates to data.

Each prototype back-end had a fully independent implementation which resulted in some amount of redundantly implemented functionality and duplicated effort for testing that functionality. This motivated a new design of the final back-ends that shares implementation wherever feasible.

### 3.3 Final Kokkos Serial, OpenMP, and CUDA implementations

The final implementions are based upon Kokkos' Serial, OpenMP, and CUDA back-ends; the OpenMP back-end replaced the Threads (raw pthreads) back-end at the request of earlyadopter application developers. These implementations share a common task DAG queue data structure and foundational operations for managing this data structure. However, due to significant differences in the underlying runtimes these implementations cannot share mechanisms for executing a task DAG.

#### 3.3.1 Managing Task DAG Queues

A task policy owns a collection of spawned tasks that are organized into multiple queues. Each queue is a simple uni-directional linked list of spawned tasks that can be efficiently updated through atomic operations. Thus each queue can be simply defined as the head of a linked list where each task is the member of a linked list, as illustrated in Figure 3.1.

Figure 3.1: Each *ready queue* is defined by the head of a linked list of tasks. Each task is a member of exactly one linked list, and is also the head of a *wait queue* of tasks and when-all entities waiting on that task. The end of each linked list is denoted by an *end* value.

A ready queue holds tasks that are ready to execute – tasks that do not have an incomplete dependence. A ready queue is defined for each priority and whether tasks in the queue are to execute on a single thread or a thread team. In Figure 3.1 a ready queue is denoted by the head of a linked list in upper left corner, and the linked list itself is denoted by the linkages labeled *next*. Thus given high, regular, and low priorities there are six ready queues each implemented by the head of a linked list.

A wait queue holds tasks and when-all entities that are waiting for execute-after dependence(s) to complete. Each task or when-all entity holds the head of a linked list of tasks (or when-all entities) waiting for that task to complete. In Figure 3.1 a wait queue is denoted by the head of a linked list in the bottom of each task or when-all entity, and the linked list itself is denoted by the linkages labeled *next*.

A given task or when-all entity will reside in at most one ready or wait queue. An *end* value is used to denote the termination of a linked list queue. Thus when the head of a ready or wait queue has the *end* value that queue is empty.

#### **Push and Pop Operations**

A linked list queue is updated with thread safe atomic push operation and almost-atomic pop operations. The push operation is applied to both ready and wait queues. The pop operation is only applied to ready queues. These operations, as summarized in Figures 3.2 and 3.3, and are shared by Kokkos' Serial, OpenMP, and CUDA implementations.

```

1

// Push 'x' to the head of the linked list

2

bool push( entity ** head , entity * x )

3

{

4

entity * y = *head ; // Query current head

while (lock != y ) {

5

6

x->next = y ; // memory fenced assignment

7

entity * z = y;

8

// Atomically attempt to replace the head of the queue,

9

// failure returns the current head.

10

y = atomic_compare_exchange(head, y, x);

if ( z == y ) return true ; // success

11

12

13

x->next = 0 ; // memory fenced assignment

14

return false ; // queue was locked

15

```

Figure 3.2: Summary of atomic push operation for updating linked list queues. The push operation pushes a new entity to the head of the linked list and the previous head becomes the next entity.

```

// Pop head from the linked list

1

\mathbf{2}

entity * pop( entity ** head )

3

// Query current head

4

entity * y = *head;

// Query current

// If queue is not empty

// If queue is not empty

while ( end != y ) {

5

if ( lock == y ) y = 0 ; // Do not attempt to re-lock a locked queue

6

\overline{7}

entity * x = y ;

// Atomically attempt to replace head of list with a lock value,

8

9

// failure returns the current head.

10

y = atomic_compare_exchange(head, y, lock);

11

if ( x == y ) { // this pop locked the queue

12

// Atomically unlock the queue by setting head to next entry.

13

atomic_exchange( head , y->next );

14

break ; // success

15

}

16

}

17

return y ;

18

```

Figure 3.3: Summary of almost-atomic pop operation for updating linked list queues. The pop operation pops the head of the linked list and the list's next entity becomes the new head.

We say the pop operation is *almost* atomic because there is a brief number of execution steps in which the head of the queue has a *lock* value. On line #10 in Figure 3.3 an attempt is made to lock the queue by atomically setting a *lock* value. If this lock succeeds then the next entry in the linked list is set to the head of the queue (Fig. 3.3 line #13) and the former head entity has been successfully popped. The lock fails when either another concurrent pop operation won the "race" to pop the head entity, or a concurrent push operation won the "race" to push a new head entity.

#### Scheduling

A task or when-all entity is scheduled by pushing it into the appropriate ready or wait queue as summarized in Figures 3.4 and 3.5. A task has at most one execute-after dependence so the scheduling operation (Fig 3.4 pushes the task into the dependence's wait queue, or if there is no dependence or the one dependence is complete pushes the task into the appropriate ready queue. A when-all entity has many dependences so the scheduling operation (Fig 3.5 attempts to push the entity into one of the incomplete dependences' wait queue. If all of the when-all entity's dependences are complete then the when-all entity transitions from waiting to complete.

```

\begin{array}{c}

1 \\

2 \\

3 \\

4 \\

5 \\

6 \\

7 \\

8 \\

9 \\

10 \\

11 \\

12 \\

\end{array}

```

1

$\frac{2}{3}$

$\frac{4}{5}$

$\frac{6}{7}$

8

9

10 11

12

13

14

$15 \\ 16$

17 18 19

```

void schedule_task( entity * x , entity * dep )

{

// Task is ready to execute if there is no execute-after dependence

// or the execute-after dependence's wait queue is locked.

bool is_ready = ( 0 == dep ) || ( ! push_task( & dep->wait , x );

if ( is_ready ) {

entity ** head = ready_queue( x ); // ready queue requested by this task

while ( ! push( head , x ) ); // Push to head of ready queue

}

}

```

Figure 3.4: A task entity is scheduled by pushing it into the execute-after dependence's wait queue or the appropriate ready queue.

Figure 3.5: A when-all entity is scheduled discovering which dependence is not complete and pushing then entity into this dependence's wait queue. If an incomplete dependence is not discovered then the when-all dependence is complete.

When a task entity completes executing, or when all dependences of a when-all entity become complete, then the entity's waiting entities must be removed from the wait queue and re-scheduled as summarized in Figure 3.6. This state transition is performed on exactly one thread that has exclusive access to the entity's data wait queue. Thus removing entities from a wait queue does not need to apply the almost-atomic pop operation.

When task or when-all entity's wait queue is locked (Fig 3.6 line #5) then that entity is observably in the complete state. When an entity is complete then new execute-after dependences are not allowed to be added to that entity. Thus the push operation will fail for that entity's locked wait queue as per line #5 in Figure 3.2.

```

1

void complete( entity * x )

\mathbf{2}

3

// Atomically obtain the head of the wait gueue and

4

// lock the wait queue against subsequent push operations.

5

entity * y = atomic_exchange( & x->wait , lock );

\mathbf{6}

if ( y != lock ) { // Succeeded in locking the wait queue

7

8

// This 'x' entity is complete so run its wait queue

9

// and re-schedule each entity that had an execute-after dependence.

while ( y != end ) {

10

entity * next = atomic_exchange( & y->next , 0 );

11

schedule( y );

12

13

y = next ;

14

15

}

16

}

```

Figure 3.6: When a task or when-all entity becomes complete all waiting entities are rescheduled.

#### Spawn, respawn, and creating a when-all

A spawn operation accepts a user's closure and a small set of scheduling parameters (Fig. 2.3 lines #7 and 28-29). Memory is allocated for the task from a memory pool (Section 3.4), the user's input closure is copied into that memory, task scheduling parameters are set, and the task is scheduled into a queue (Fig. 3.4).

A respawn operation is called by a task's execute function and accepts the executing task's this pointer and a small set of rescheduling parameters (Fig. 2.3 line #30). The task's scheduling parameters are updated and when the task's execute function returns the task is rescheduled into a queue (Fig. 3.4).

The create when-all operation accepts a set of execute-after dependences (Fig. 2.3 line #30). Memory is allocated for the when-all entity, input dependences are copied into this memory, and the when-all entity is scheduled into a queue (Fig. 3.5).

#### 3.3.2 Executing a Task DAG

The task DAG queue data structure and queue-management operations are shared by Kokkos' Serial, OpenMP, and CUDA implementations. However, the mechanisms for executing tasks on these back-ends are significantly different. These differences are divided into *driver* mechanisms and *thread team* mechanisms.

#### CPU Serial "thread team" and driver

Kokkos' Serial "thread team" implementation is trivial as the team size is fixed at one. The task DAG execution driver is almost as trivial; ready queues are iterated in priority order, tasks are popped from a ready queue their execute functions are called, and the driver loops until all ready queues are empty.

Since there is only one thread executing the driver function new tasks could be spawned without an opportunity for existing ready tasks to execute. Such a scenario can lead to the task DAG having the maximum memory high-water-mark for allocated tasks. To mitigate this scenario the Serial implemention's spawn operation will execute any ready tasks before allocating memory for the to-be-spawned task. When these tasks complete and their futures are destroyed memory allocated for tasks is deallocated, freeing space for the spawned task to be allocated and reducing the potential memory high-water-mark.

#### CPU OpenMP thread teams

On multicore CPU and manycore Intel Xeon Phi architectures tasks may execute on thread teams. We assume that a task DAG algorithm will have a large number of potentially concurrent tasks where each task has a modest amount of internal data parallelism (recall Section 2.2.8). On CPU-like architectures each task is executed on a core and any hyper-threads on that core define a thread team for the task. Thus an executing task has exclusive access to per-core CPU resources such as L1 data and instruction caches.

#### CPU OpenMP thread team barrier

Barrier synchronization of a thread team is a performance critical operation. Team barriers are used to synchronize thread teams' use of shared memory, perform thread team collective operations such as parallel reduce and scan operations, and within the task DAG execution driver. We use the barrier algorithm summarized in Figure 3.7 which minimizes the number of shared variables accessed and minimizes writes to those shared variables.

The variable sync\_shared is a cache-aligned array of two 64bit integer values that is shared by the team. Within each call to team\_barrier each thread team member writes exactly one byte within this array to a designated value, and then spin waits for all team members to write their respective bytes. The synchronization variable alternates between calls to team\_barrier and the synchronization value is flipped every other call.

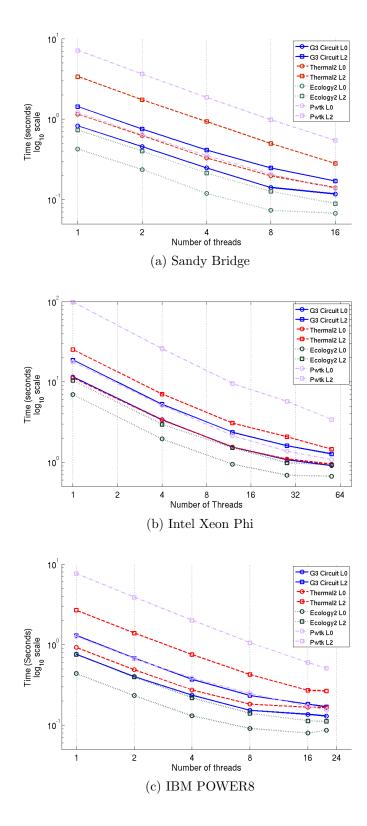

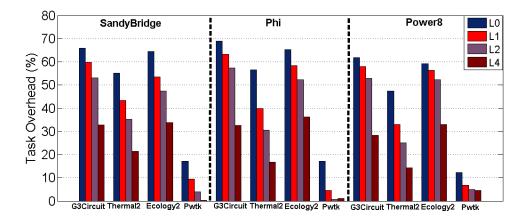

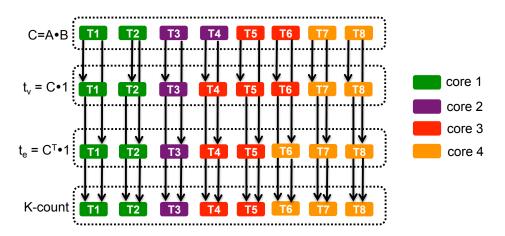

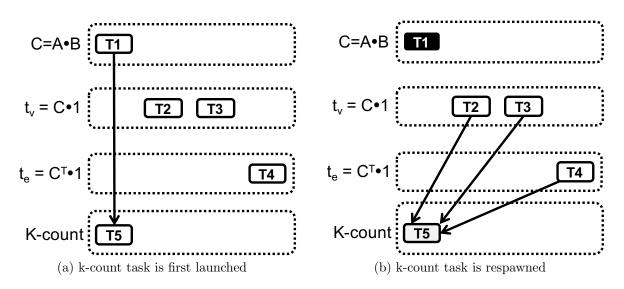

#### CPU OpenMP driver