Traleika Glacier

From Modelado Foundation

| Traleika Glacier X-Stack | |

|---|---|

| |

| Team Members | Intel, Reservoir Labs, ETI, UDEL, UC San Diego, Rice U., UIUC, PNNL |

| PI | Shekhar Borkar (Intel) |

| Co-PIs | Wilf Pinfold (Intel), Richard Lethin (Reservoir Labs), Laura Carrington (UC San Diego), Vivek Sarkar (Rice U.), David Padua (UIUC), Josep Torrellas (UIUC), Andres Marquez (PNNL) |

| Website | https://xstack.exascale-tech.com/wiki/index.php/Main_Page |

| Download | {{{download}}} |

Team Members

- Intel: Shekhar Borkar (PI); Hardware guidance, HW/SW co-design, resiliency, technical management

- Reservoir Labs: Richard Lethin (PI); Programming system, R-Stream, tools, optimization

- University of California, San Diego (UC San Diego): Laura Carrington (PI); Applications

- Rice University: Vivek Sarkar (PI); Programming system, runtime system

- University of Illinois at Urbana-Champaign (UIUC): David Padua, Josep Torrellas (PIs); Programming system, Hierarchical Tiles Arrays (HTA), architecture, system architecture evaluation

- Pacific Northwest National Laboratory (PNNL): Andres Marquez (PI); Kernels and proxy apps for evaluation

Goals and Objectives

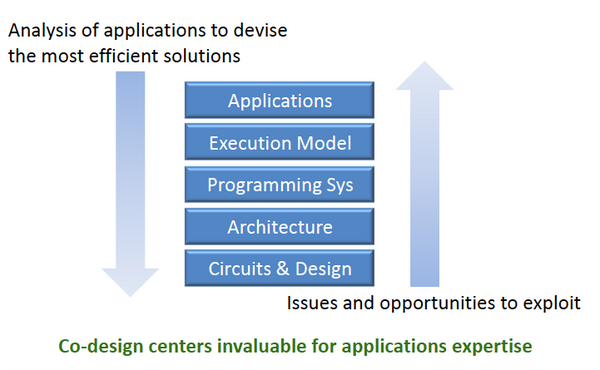

Goal: The Traleika Glacier X-Stack program will develop X-Stack software components in close collaboration with application specialists at the DOE co-design centers and with the best available knowledge of the Exascale systems we anticipate will be available in 2018/2020.

Description: Intel has built a straw-man hardware platform that embodies potential technology solutions to well understood challenges. This straw-man is implemented in the form of a simulator that will be used as a tool to test software components under investigation by Traleika team members. Co-design will be achieved by developing representative application components that stress software components and platform technologies and then use these stress tests to refine platform and software elements iteratively to an optimum solution. All software and simulator components will be developed in open source facilitating open cross team collaboration. The interface between the software components and the simulator will be built to facilitate back end replacement with current production architectures (MIC and Xeon) providing a broadly available software development vehicle and facilitating the integration of new tools and compilers conceived and developed under this proposal with existing environments like MPI, OpenMP, and OpenCL.

The Traleika Glacier X-Stack team brings together strong technical expertise from across the exascale software stack. Utilizing applications of high interest to the DoE from five National Labs, coupled with software systems expertise from Reservoir Labs, ET International, the University of Illinois, University of California San Diego, University of Delaware, and Rice University, using a foundation of platform excellence from Intel. This project builds collaboration between many of the partners making this team uniquely capable of rapid progress. The research is not only expected to further the art in system software for high performance computing but also provide invaluable feedback thru the co-design loop for hardware design and application development. By breaking down research and development barriers between layers in the solution stack this collaboration and the open tools it produces will spur innovation for the next generation of high performance computing systems.

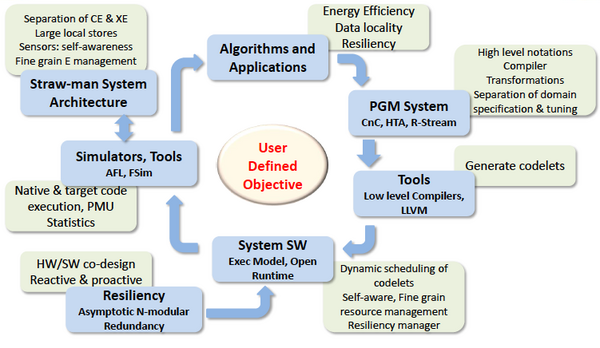

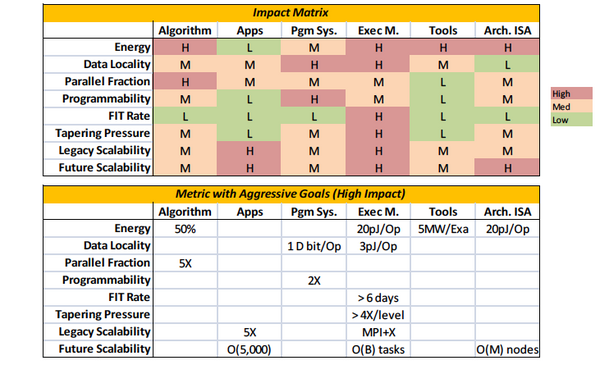

Objectives:

- Energy efficiency: SW components interoperate, harmonize, exploit HW features, and optimize the system for energy efficiency

- Data locality: PGM system & system SW optimize to reduce data movement

- Scalability: SW components scalable, portable to O(109)—extreme parallelism

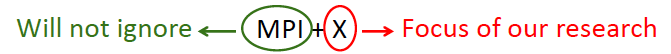

- Programmability: New (Asychronous) & legacy (MPI+OpenMP), with gentle slope for productivity

- Execution model: Objective function based, dynamic, global system optimization

- Self-awareness: Dynamically respond to changing conditions and demands

- Resiliency: Asymptotically provide reliability of N-modular redundancy using HW/SW co-design; HW detection, SW correction

Status Reports

- Traleika Glacier X-Stack Highlights, April 1, 2014

- Traleika Glacier X-Stack Status Review, March 25, 2014

- Traleika Glacier Year 2 Interim Status Report, March 12, 2014

- Traleika Glacier Year 2 Progress Report, May 30, 2014

- Traleika Glacier Milestone 8 Report, September 1, 2014

- Traleika Glacier Milestone 9 Report, December 8, 2014

- Traleika Glacier Milestone 10 Report, March 2, 2015

- Traleika Glacier Milestone 11 Report, June 2, 2014

Meetings and Presentations

Weekly Extreme Scale Deep-Dive: Schedule and Archive

- Weekly Technical Review Meeting (Tuesdays, 10-12 Pacific Time)

Co-Design Workshops (Newest to Oldest)

- Application Workshop 5 - September 29, 2015 - October 1, 2015

- Application Workshop 4 - April 7-8, 2015

- Application Workshop 3 - September 30, 2014 - October 2, 2014

- Application Workshop 2 - January 21-23, 2014

Traleika Glacier products

Research Products

Software Releases

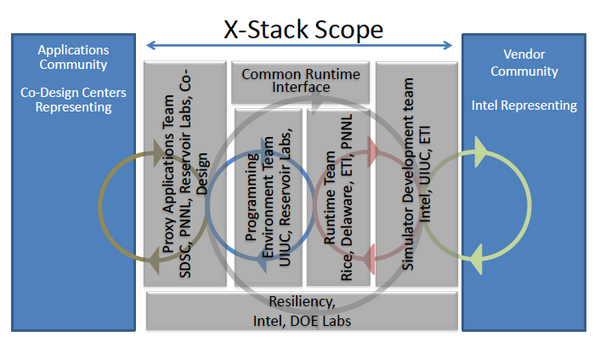

Scope of the Project

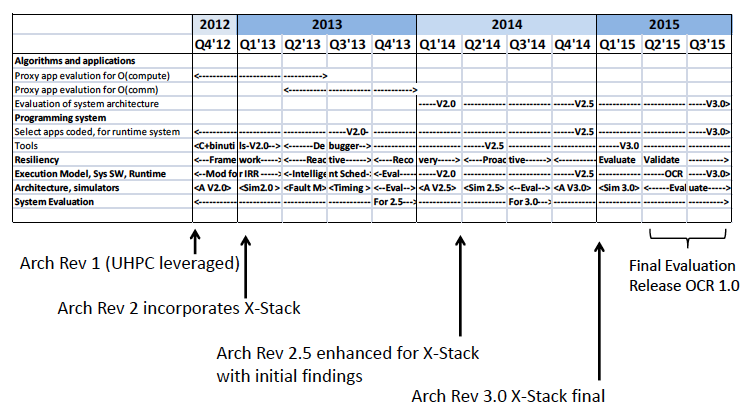

Roadmap

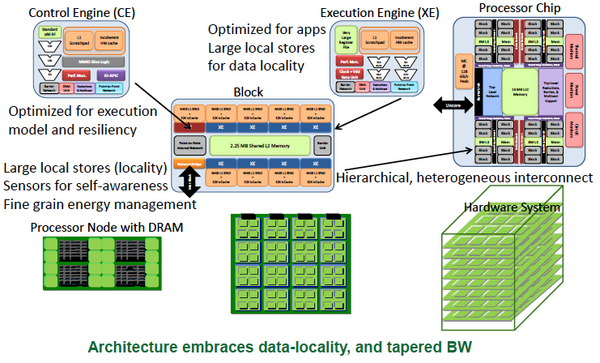

Architecture

Straw-man System Architecture and Evaluation

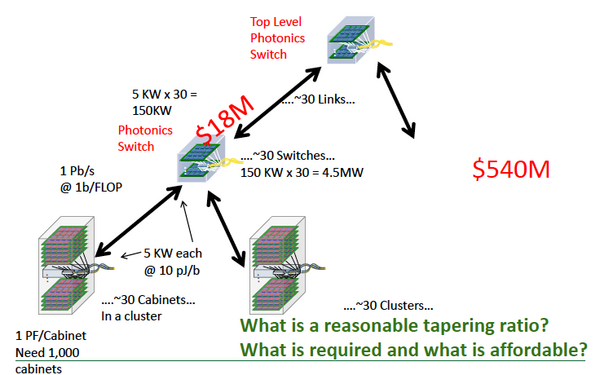

Data-locality and BW Tapering, Why So Important?

Programming and Execution Models

Programming model

- Separation of concerns: Domain specification & HW mapping

- Express data locality with hierarchical tiling

- Global, shared, non-coherent address space

- Optimization and auto generation of codelets (HW specific)

Execution model

- Dataflow inspired, tiny codelets (self contained)

- Dynamic, event-driven scheduling, non-blocking

- Dynamic decision to move computation to data

- Observation based adaption (self-awareness)

- Implemented in the runtime environment

Separation of concerns

- User application, control, and resource management

Programming System Components

Runtime

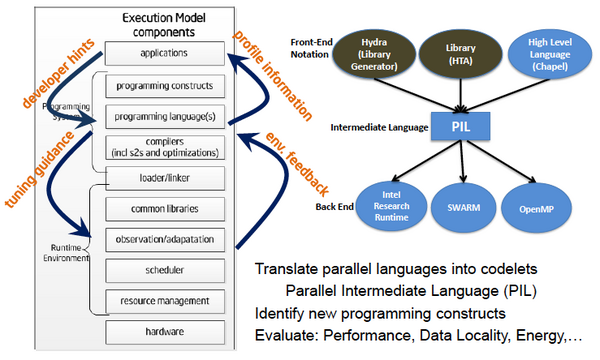

- Different runtimes target different aspects

- IRR: targeted for Intel Straw-man architecture

- SWARM: runtime for a wide range of parallel machines

- DAR3TS: explore codelet PXM using portable C++

- Habanero-C: interfaces IRR, tie-in to CnC

- All explore related aspects of the codelet Program Exec Model (PXM)

- Goal: Converge towards Open Collaborative Runtime (OCR)

- Enabling technology development for codelet execution

- Model systems, foster novel runtime systems research

- Greater visibility through SW stack -> efficient computing

- Break OS/Runtime information firewall

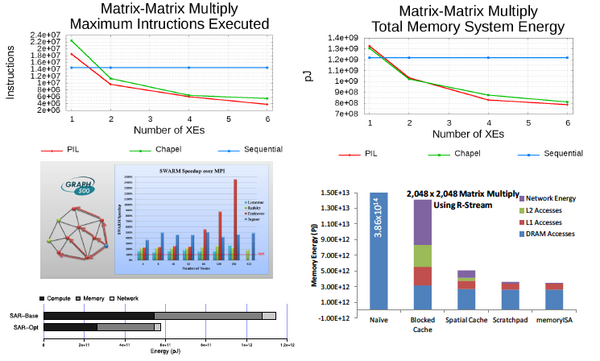

Some Promising Results:

Runtime Research Agenda

- Locality aware scheduling—heuristics for locality/E-efficiency

- Extensions to standard Habanero-C runtime

- Adaptive boosting and idling of hardware

- Avoid energy expensive unsuccessful steals that perform no work

- Turbo mode for a core executing serial code

- Fine grain resource (including energy) management

- Dynamic data-block movement

- Co-locate codelets and data

- Move codelets to data

- Introspection and dynamic optimization

- Performance counters, sensors provide real time information

- Optimization of the system for user defined objective

- (Go beyond energy proportional computing)

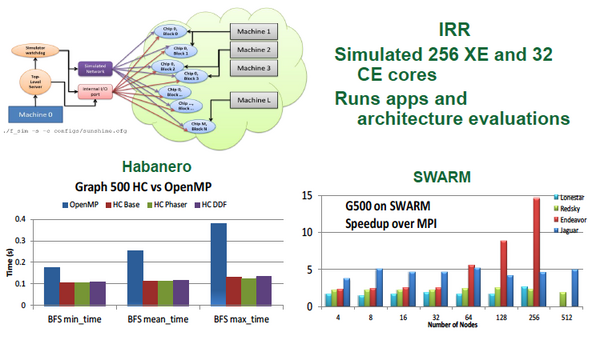

Simulators and Tools

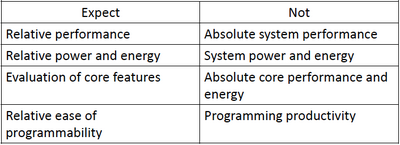

Simulators—what to expect and not

- Evaluation of architecture features for PGM and EXE models

- Relative comparison of performance, energy

- Data movement patterns to memory and interconnect

- Relative evaluation of resource management techniques

Results Using Simulators

Applications and HW-SW Codesign

X-Stack Components